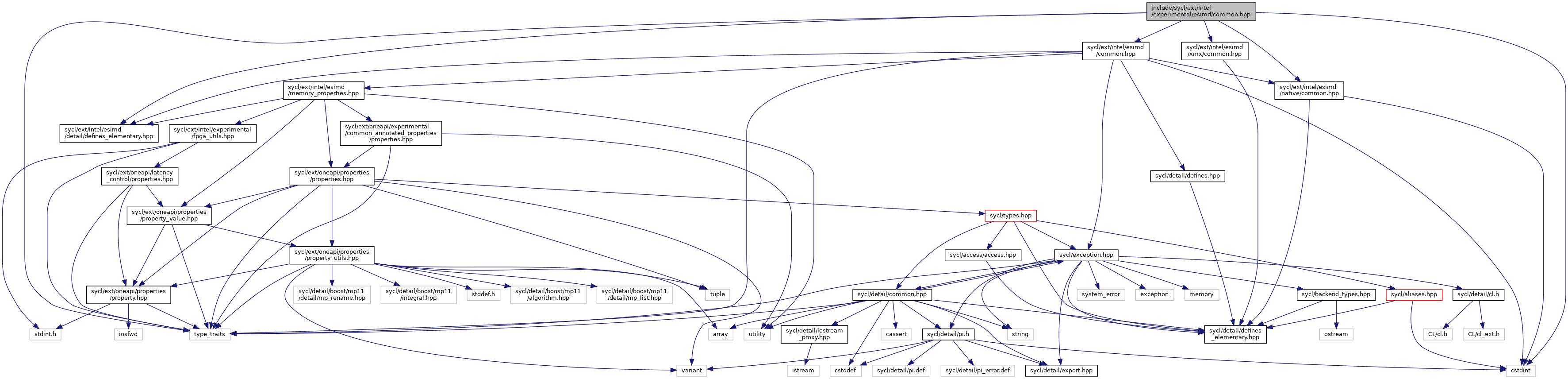

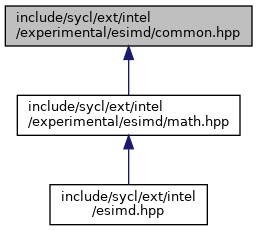

#include <sycl/ext/intel/esimd/common.hpp>#include <sycl/ext/intel/esimd/detail/defines_elementary.hpp>#include <sycl/ext/intel/esimd/native/common.hpp>#include <sycl/ext/intel/esimd/xmx/common.hpp>#include <cstdint>#include <type_traits>

Go to the source code of this file.

Classes | |

| struct | sycl::_V1::ext::intel::experimental::esimd::detail::lsc_expand_type< T > |

Namespaces | |

| sycl | |

| sycl::_V1 | |

| sycl::_V1::ext | |

| sycl::_V1::ext::intel | |

| sycl::_V1::ext::intel::experimental | |

| sycl::_V1::ext::intel::experimental::esimd | |

| sycl::_V1::ext::intel::experimental::esimd::detail | |

Typedefs | |

| using | sycl::_V1::ext::intel::experimental::esimd::lsc_data_size = __ESIMD_DNS::lsc_data_size |

| using | sycl::_V1::ext::intel::experimental::esimd::detail::lsc_vector_size = __ESIMD_DNS::lsc_vector_size |

| using | sycl::_V1::ext::intel::experimental::esimd::detail::lsc_data_order = __ESIMD_DNS::lsc_data_order |

| using | sycl::_V1::ext::intel::experimental::esimd::cache_hint = sycl::ext::intel::esimd::cache_hint |

| L1 or L2 cache hint kinds. More... | |

Enumerations | |

| enum class | sycl::_V1::ext::intel::experimental::esimd::split_barrier_action : uint8_t { sycl::_V1::ext::intel::experimental::esimd::wait = 0 , sycl::_V1::ext::intel::experimental::esimd::signal = 1 } |

| Represents a split barrier action. More... | |

Functions | |

| template<lsc_vector_size VS> | |

| constexpr void | sycl::_V1::ext::intel::experimental::esimd::detail::check_lsc_vector_size () |

| template<typename T , lsc_data_size DS> | |

| constexpr void | sycl::_V1::ext::intel::experimental::esimd::detail::check_lsc_data_size () |

| template<lsc_vector_size VS> | |

| constexpr uint8_t | sycl::_V1::ext::intel::experimental::esimd::detail::to_int () |

| template<int VS> | |

| constexpr lsc_vector_size | sycl::_V1::ext::intel::experimental::esimd::detail::to_lsc_vector_size () |

| template<typename T , lsc_data_size DS> | |

| constexpr lsc_data_size | sycl::_V1::ext::intel::experimental::esimd::detail::finalize_data_size () |

| constexpr lsc_data_size | sycl::_V1::ext::intel::experimental::esimd::detail::expand_data_size (lsc_data_size DS) |