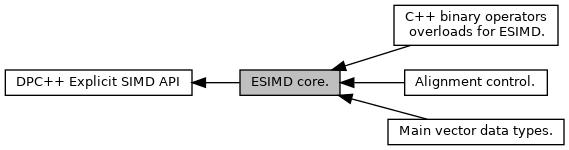

Core APIs defining main vector data types and their interfaces. More...

Modules | |

| C++ binary operators overloads for ESIMD. | |

Standard C++ binary operators overloads applicable to simd_obj_impl derivatives - simd , simd_mask , simd_view and their combinations. | |

| Alignment control. | |

| Alignment type tags and related APIs for use with ESIMD memory access operations. | |

| Main vector data types. | |

| ESIMD defines the following two main vector data types: | |

Classes | |

| struct | sycl::_V1::ext::intel::esimd::saturation_on_tag |

| Gen hardware supports applying saturation to results of certain operations. More... | |

| struct | sycl::_V1::ext::intel::esimd::saturation_off_tag |

| This type tag represents "saturation off" behavior. More... | |

Typedefs | |

| using | sycl::_V1::ext::intel::esimd::uchar = unsigned char |

| using | sycl::_V1::ext::intel::esimd::ushort = unsigned short |

| using | sycl::_V1::ext::intel::esimd::uint = unsigned int |

| using | sycl::_V1::ext::intel::esimd::SurfaceIndex = unsigned int |

| Surface index type. More... | |

| using | sycl::_V1::ext::intel::experimental::esimd::lsc_data_size = __ESIMD_DNS::lsc_data_size |

| using | sycl::_V1::ext::intel::experimental::esimd::cache_hint = sycl::ext::intel::esimd::cache_hint |

| L1 or L2 cache hint kinds. More... | |

Functions | |

| constexpr int | sycl::_V1::ext::intel::esimd::is_channel_enabled (rgba_channel_mask M, rgba_channel Ch) |

| constexpr int | sycl::_V1::ext::intel::esimd::get_num_channels_enabled (rgba_channel_mask M) |

Variables | |

| static constexpr saturation_off_tag | sycl::_V1::ext::intel::esimd::saturation_off {} |

| Type tag object representing "saturation off" behavior. More... | |

| static constexpr saturation_on_tag | sycl::_V1::ext::intel::esimd::saturation_on {} |

| Type tag object representing "saturation on" behavior. More... | |

Core APIs defining main vector data types and their interfaces.

| using sycl::_V1::ext::intel::experimental::esimd::cache_hint = typedef sycl::ext::intel::esimd::cache_hint |

L1 or L2 cache hint kinds.

Definition at line 72 of file common.hpp.

| using sycl::_V1::ext::intel::experimental::esimd::lsc_data_size = typedef __ESIMD_DNS::lsc_data_size |

Definition at line 28 of file common.hpp.

| using sycl::_V1::ext::intel::esimd::SurfaceIndex = typedef unsigned int |

Surface index type.

Surface is an internal representation of a memory block addressable by GPU in "stateful" memory model, and each surface is identified by its "binding table index" - surface index.

Definition at line 64 of file common.hpp.

| using sycl::_V1::ext::intel::esimd::uchar = typedef unsigned char |

Definition at line 41 of file common.hpp.

| using sycl::_V1::ext::intel::esimd::uint = typedef unsigned int |

Definition at line 43 of file common.hpp.

| using sycl::_V1::ext::intel::esimd::ushort = typedef unsigned short |

Definition at line 42 of file common.hpp.

|

strong |

Represents an atomic operation.

Operations always return the old value(s) of the target memory location(s) as it was before the operation was applied. Each operation is annotated with a pseudocode illustrating its semantics, addr is a memory address (one of the many, as the atomic operation is vector) the operation is applied at, src0 is its first argumnet, src1 - second. Using the floating point atomic operations adds the requirement to running the code with it on target devices with LSC features (ACM, PVC, etc).

Definition at line 160 of file common.hpp.

|

strong |

Specify if end of thread should be set.

| Enumerator | |

|---|---|

| not_eot | |

| eot | |

Definition at line 67 of file common.hpp.

|

strong |

Specify if sendc should be used.

| Enumerator | |

|---|---|

| not_sendc | |

| sendc | |

Definition at line 73 of file common.hpp.

|

strong |

|

strong |

Represents a pixel's channel mask - all possible combinations of enabled channels.

| Enumerator | |

|---|---|

| R | |

| G | |

| GR | |

| B | |

| BR | |

| BG | |

| BGR | |

| A | |

| AR | |

| AG | |

| AGR | |

| AB | |

| ABR | |

| ABG | |

| ABGR | |

Definition at line 122 of file common.hpp.

|

strong |

|

constexpr |

Definition at line 145 of file common.hpp.

References sycl::_V1::ext::intel::esimd::A, sycl::_V1::ext::intel::esimd::B, sycl::_V1::ext::intel::esimd::G, sycl::_V1::ext::intel::esimd::is_channel_enabled(), and sycl::_V1::ext::intel::esimd::R.

|

constexpr |

Definition at line 140 of file common.hpp.

Referenced by sycl::_V1::ext::intel::esimd::get_num_channels_enabled().

|

inlinestaticconstexpr |

Type tag object representing "saturation off" behavior.

Definition at line 53 of file common.hpp.

|

inlinestaticconstexpr |

Type tag object representing "saturation on" behavior.

Definition at line 56 of file common.hpp.