The 'cache_hint_L1', 'cache_hint_L2' and 'cache_hint_L3' properties are used to specify L1, L2, L3 cache hints available in target device. More...

#include <sycl/ext/intel/esimd/memory_properties.hpp>

Public Types | |

| template<cache_hint Hint> | |

| using | value_t = ext::oneapi::experimental::property_value< cache_hint_L1_key, std::integral_constant< cache_hint, Hint > > |

Additional Inherited Members | |

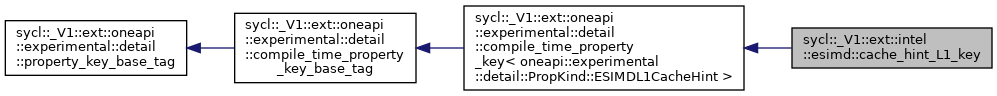

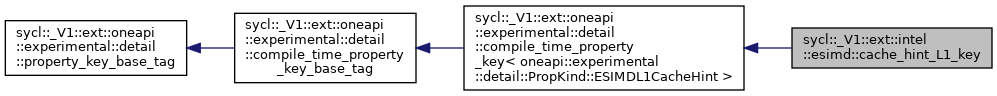

Static Protected Attributes inherited from sycl::_V1::ext::oneapi::experimental::detail::compile_time_property_key< oneapi::experimental::detail::PropKind::ESIMDL1CacheHint > Static Protected Attributes inherited from sycl::_V1::ext::oneapi::experimental::detail::compile_time_property_key< oneapi::experimental::detail::PropKind::ESIMDL1CacheHint > | |

| static constexpr PropKind | Kind |

The 'cache_hint_L1', 'cache_hint_L2' and 'cache_hint_L3' properties are used to specify L1, L2, L3 cache hints available in target device.

L1 cache is usually the fastest memory closest to the processor. L2 is the next level cache (slower and farther from the processor), etc. L2 cache hint property must be used for the old/experimental LSC L3 cache hints. L3 cache property is reserved for future devices.

Definition at line 107 of file memory_properties.hpp.

| using sycl::_V1::ext::intel::esimd::cache_hint_L1_key::value_t = ext::oneapi::experimental::property_value< cache_hint_L1_key, std::integral_constant<cache_hint, Hint> > |

Definition at line 111 of file memory_properties.hpp.