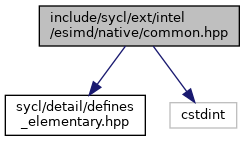

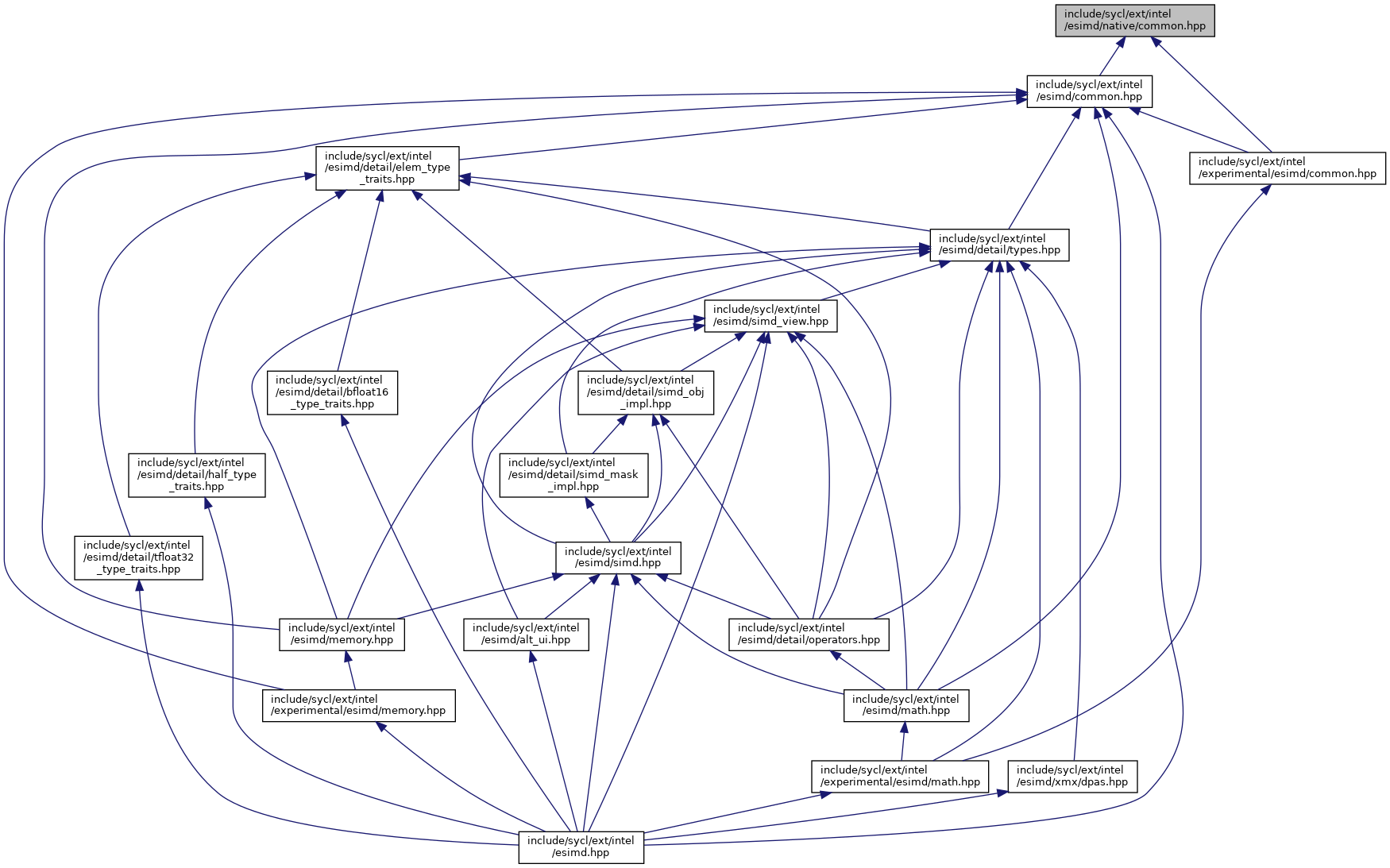

Go to the source code of this file.

|

| enum class | sycl::_V1::ext::intel::esimd::native::lsc::atomic_op : uint8_t {

sycl::_V1::ext::intel::esimd::native::lsc::inc = 0x08

, sycl::_V1::ext::intel::esimd::native::lsc::dec = 0x09

, sycl::_V1::ext::intel::esimd::native::lsc::load = 0x0a

, sycl::_V1::ext::intel::esimd::native::lsc::store = 0x0b

,

sycl::_V1::ext::intel::esimd::native::lsc::add = 0x0c

, sycl::_V1::ext::intel::esimd::native::lsc::sub = 0x0d

, sycl::_V1::ext::intel::esimd::native::lsc::smin = 0x0e

, sycl::_V1::ext::intel::esimd::native::lsc::smax = 0x0f

,

sycl::_V1::ext::intel::esimd::native::lsc::umin = 0x10

, sycl::_V1::ext::intel::esimd::native::lsc::umax = 0x11

, sycl::_V1::ext::intel::esimd::native::lsc::cmpxchg = 0x12

, sycl::_V1::ext::intel::esimd::native::lsc::fadd = 0x13

,

sycl::_V1::ext::intel::esimd::native::lsc::fsub = 0x14

, sycl::_V1::ext::intel::esimd::native::lsc::fmin = 0x15

, sycl::_V1::ext::intel::esimd::native::lsc::fmax = 0x16

, sycl::_V1::ext::intel::esimd::native::lsc::fcmpxchg = 0x17

,

sycl::_V1::ext::intel::esimd::native::lsc::bit_and = 0x18

, sycl::_V1::ext::intel::esimd::native::lsc::bit_or = 0x19

, sycl::_V1::ext::intel::esimd::native::lsc::bit_xor = 0x1a

} |

| | LSC atomic operation codes. More...

|

| |