Introduction

This paper describes the Compress and Verify feature employed in Intel® QuickAssist Technology products. The paper includes an overview of the feature, including its purpose. It describes the tests used to determine correctness, as well as the detailed description of a study undertaken to verify the design assumptions of the feature.

Acronyms

CnV |

Compress and Verify |

CRC |

Cyclic Redundancy Check |

DMA |

Direct Memory Access |

DRAM |

Dynamic Random Access Memory |

e2e |

End-to-end |

ME |

Microengine |

QAT |

Intel QuickAssist Technology |

Background

Compress and Verify (CnV) is a feature of Intel® QuickAssist Technology (Intel® QAT) which allows assurance that a dataset being compressed using Intel® QAT hardware can be correctly decompressed later. Compress and Verify is designed to detect invalid encodings of literals, lengths, or distance codes by replaying the compressed data through a decompression engine.

This paper specifically addresses the 2.0 a/b/c version of Intel® QAT, which is integrated into Sapphire Rapids, Emerald Rapids and Granite Rapids processors, as well as other processors.

Compression Offload Described

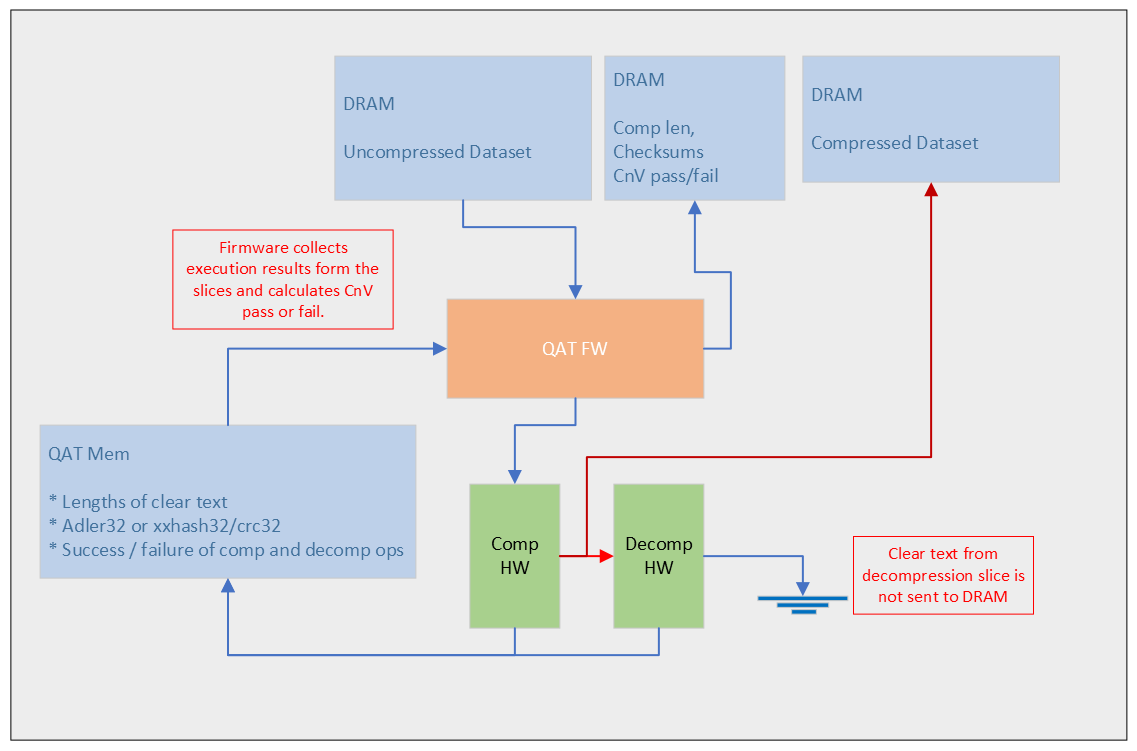

When a compress operation is submitted to Intel® QAT as a stand-alone operation, the basic steps are:

The compress request is submitted to Intel® QAT for compression via a hardware ring.

A compression engine is allocated for the compress component of CnV.

A decompression engine is allocated for the verify component of CnV.

The dataset is moved via Direct Memory Access (DMA) from memory to the QAT complex.

The cleartext of the dataset is fed to the compress engine

Compressed data from the compress engine is moved to DRAM.

Compressed data from the compress engine is fed to the decompress engine.

At completion, the Microengine (ME) collects the available data and verifies the request or marks the request as failed.

Pictorially, this looks like:

The compression hardware and decompression hardware have separate engines for computing the checksums on the cleartext of the dataset. This prevents errors in the calculation of checksums in the compression block being replicated in the decompression block.