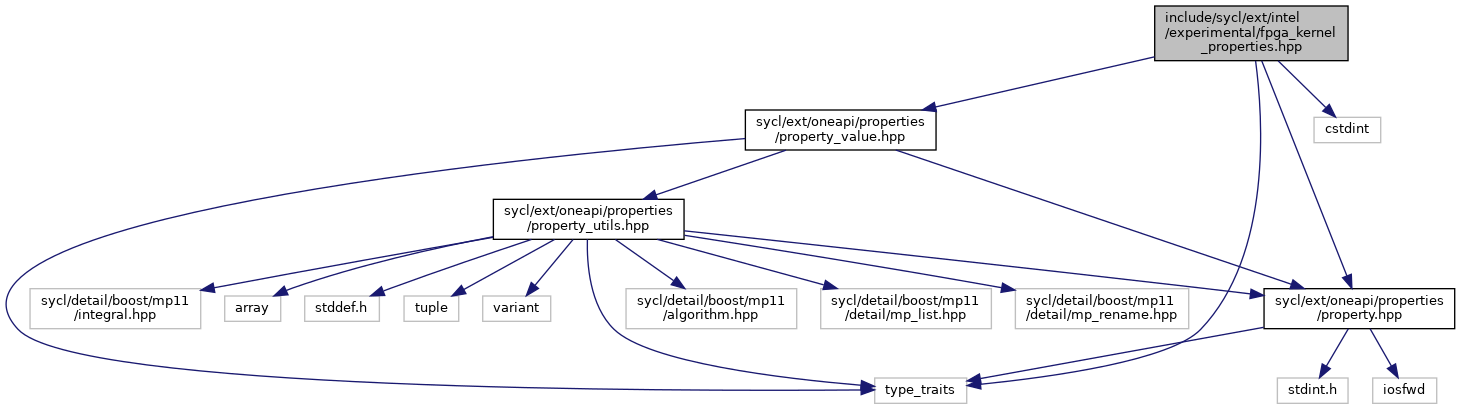

#include <sycl/ext/oneapi/properties/property.hpp>#include <sycl/ext/oneapi/properties/property_value.hpp>#include <cstdint>#include <type_traits>

Go to the source code of this file.

Variables | |

| template<streaming_interface_options_enum option = streaming_interface_options_enum::accept_downstream_stall> | |

| constexpr streaming_interface_key::value_t< option > | sycl::_V1::ext::intel::experimental::streaming_interface |

| constexpr streaming_interface_key::value_t< streaming_interface_options_enum::accept_downstream_stall > | sycl::_V1::ext::intel::experimental::streaming_interface_accept_downstream_stall |

| constexpr streaming_interface_key::value_t< streaming_interface_options_enum::remove_downstream_stall > | sycl::_V1::ext::intel::experimental::streaming_interface_remove_downstream_stall |

| template<register_map_interface_options_enum option = register_map_interface_options_enum::do_not_wait_for_done_write> | |

| constexpr register_map_interface_key::value_t< option > | sycl::_V1::ext::intel::experimental::register_map_interface |

| constexpr register_map_interface_key::value_t< register_map_interface_options_enum::wait_for_done_write > | sycl::_V1::ext::intel::experimental::register_map_interface_wait_for_done_write |

| constexpr register_map_interface_key::value_t< register_map_interface_options_enum::do_not_wait_for_done_write > | sycl::_V1::ext::intel::experimental::register_map_interface_do_not_wait_for_done_write |

| template<int pipeline_directive_or_initiation_interval = -1> | |

| constexpr pipelined_key::value_t< pipeline_directive_or_initiation_interval > | sycl::_V1::ext::intel::experimental::pipelined |

| template<fpga_cluster_options_enum option = fpga_cluster_options_enum::stall_free> | |

| constexpr fpga_cluster_key::value_t< option > | sycl::_V1::ext::intel::experimental::fpga_cluster |

| constexpr fpga_cluster_key::value_t< fpga_cluster_options_enum::stall_free > | sycl::_V1::ext::intel::experimental::stall_free_clusters |

| constexpr fpga_cluster_key::value_t< fpga_cluster_options_enum::stall_enable > | sycl::_V1::ext::intel::experimental::stall_enable_clusters |